#### (19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11)特許番号

特許第3210054号 (P3210054)

Z

$\mathbf{Z}$

(45)発行日 平成13年9月17日(2001.9.17)

(24)登録日 平成13年7月13日(2001.7.13)

(51) Int.Cl.7

識別記号

F I

G 0 6 G 7/48

G 0 6 G 7/48

G 0 6 F 17/10

G 0 6 F 15/31

請求項の数8(全20頁)

(21)出願番号 特願平4-35042

(22)出願日 平成4年2月21日(1992.2.21)

(65)公開番号 特開平5-233857

(43)公開日 平成5年9月10日(1993.9.10) 審査請求日 平成9年7月29日(1997.7.29) (73)特許権者 591018497

山川 烈

福岡県飯塚市大字幸袋781番地300

(72)発明者 山川 烈

福岡県飯塚市大字幸袋781番地300

(74)代理人 100081503

弁理士 金山 敏彦 (外2名)

審査官 日下 善之

(56)参考文献 特開 平1-147657 (JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G06G 7/48 G06F 17/10

## (54) 【発明の名称】 カオス的信号発生装置および方法ならびにカオス・ディバイス

1

## (57)【特許請求の範囲】

【請求項1】 入力信号を所定時間ずつ順次遅延させる 複数のディレイ手段, 上記ディレイ手段のうちの少な くとも1つから得られる信号を非線形関数によって変換 する非線形関数手段,

上記ディレイ手段の他のものから得られる信号を所定係 数倍する係数手段,

上記非線形関数手段および係数手段から得られる信号を 加算する加算手段,ならびに動作開始時に上記ディレイ 手段,または上記非線形関数手段および係数手段,また 10 は上記加算手段に初期値を与える初期化手段を備え,

上記加算手段の出力が最前段の上記ディレイ手段にフィードバックされるように構成されている,カオス的信号 発生装置。

【請求項2】 入力信号を微小時間ずつ順次遅延させる

2

複数のディレイ回路, 上記ディレイ回路のうちの少なくとも1つから得られる信号を非線形関数によって変換する非線形関数回路,

上記ディレイ回路の他のものから得られる信号を所定係 数倍する係数回路,

上記非線形関数回路および係数回路から得られる信号を 加算する加算回路,ならびに動作開始時に上記ディレイ 回路,または上記非線形関数回路および係数回路,また は上記加算回路に初期値を与える初期化回路を備え,

10 上記加算回路の出力が最前段の上記ディレイ回路にフィードバックされるように構成されている,カオス・ディバイス。

【請求項3】 順次与えられる複数個の信号をその順序 に保存しておき,

保存されている信号のうちの少なくとも1つを非線形関

数によって変換し.

保存されている信号の他のものを所定係数倍し,

非線形関数変換された信号および所定係数倍された信号 を加算し,

加算により得られた信号を最新の信号として保存しかつ 保存されている信号を順次シフトする,

上記一連の処理を初期値を与えることにより開始させか つ繰返させることによりカオス的信号を得る,カオス的 信号発生方法。

【請求項4】 入力信号を所定時間ずつ順次遅延させる 10 複数のディレイ手段, 上記ディレイ手段から得られる 信号をそれぞれ所定の非線形関数によって変換する複数 の非線形関数手段,

上記複数の非線形関数手段から得られる信号を加算する 加算手段,ならびに動作開始時に上記ディレイ手段また は上記非線形関数手段にそれぞれ初期値を与える初期化 手段を備え,

上記加算手段の出力が最前段の上記ディレイ手段にフィードバックされるように構成されている,カオス的信号 発生装置。

【請求項5】 入力信号を微小時間ずつ順次遅延させる 複数のディレイ回路, 上記ディレイ回路から得られる 信号をそれぞれ所定の非線形関数によって変換する複数 の非線形関数回路.

上記複数の非線形関数回路から得られる信号を加算する 加算回路,ならびに動作開始時に上記ディレイ回路また は上記非線形関数回路にそれぞれ初期値を与える初期化 回路を備え,

上記加算回路の出力が最前段の上記ディレイ回路にフィードバックされるように構成されている,カオス・ディ 30 バイス。

【請求項6】 順次与えられる複数個の信号をその順序に保存しておき,

保存されている信号をそれぞれ所定の非線形関数によって変換し,

非線形関数変換された信号を加算し、

加算により得られた信号を最新の信号として保存しかつ 保存されている信号を順次シフトする,

上記一連の処理を初期値を与えることにより開始させか なカオス的な時間的ふるまいをする つ繰返させることによりカオス的信号を得る,カオス的 40 および方法を提供するものである。 【0007】第1の発明は非線形限

【請求項7】 複数の入力変数信号をそれぞれ所定時間 遅延させる複数のディレイ手段,

上記複数のディレイ手段から得られる複数の変数信号のうちの少なくとも1つをそれぞれ入力とし,この入力変数信号を1変数または多変数非線形関数により関数信号に変換する複数の非線形関数手段,ならびに各入力変数信号の初期値を与える複数の初期化手段を備え,

上記非線形関数手段から得られる関数信号が対応する上 を所定係数倍する係数手段,上記非線形関数手段および記ディレイ手段にフィードバックされるように構成され 50 係数手段から得られる信号を加算する加算手段,ならび

ている,カオス的信号発生装置。

【請求項8】 複数の入力変数信号をそれぞれ保存しておき,

保存されている複数の変数信号のうちのいくつかを複数 の異なる多変数非線形関数によりそれぞれ関数信号に変 換し,

多変数非線形関数変換により得られた複数の関数信号を 新たな入力変数信号としてそれぞれ保存する,

上記一連の処理を初期値を与えることにより開始させか つ繰返させることにより複数のカオス的信号を得る,カ オス的信号発生方法。

【発明の詳細な説明】

[0001]

【技術分野】この発明は,カオス的信号発生装置および 方法ならびにカオス・ディバイスに関する。

【0002】この明細書において信号とは,アナログ信号,2値信号,バイナリィ・ディジタル・データ等を含む概念である。

[0003]

20 【背景技術】数学の分野において,物理学において,コンピュータ・サイエンスにおいて,他の様々の分野においてカオス(Chaos)の理論的,実証的研究が盛んになりつつある。カオス理論は,情報処理,セルオートマトン等のコンピュータ・サイエンス,気象(天気予報),地震等の複雑な自然現象の予知,その他に応用できる可能性があるともいわれているが,未だ模索の段階にある。

【0004】カオスに関する文献としては次のようなものがある。

) 【 0 0 0 5 】合原一幸編著「カオス - カオス理論の基礎 と応用」(株)サイエンス社,1990

「数理科学」1981年11月号(NO.221)および1989年5月号(NO.311),(株)サイエンス社

「Computer Today」1989年7月号(NO.32)および1989年9月号(NO.33), (株)サイエンス社

[0006]

【発明の開示】この発明は,カオスの理論的および実証的研究のために必要な,さらに表示,その他に応用可能なカオス的な時間的ふるまいをする信号を発生する装置および方法を提供するものである。

【0007】第1の発明は非線形関数要素と線形関数要素とを含む基本的なカオス的信号発生装置(またはカオス・ディバイス)および方法を提供するものである。

【0008】第1の発明によるカオス的信号発生装置は,入力信号を所定時間ずつ順次遅延させる複数のディレイ手段,上記ディレイ手段のうちの少なくとも1つから得られる信号を非線形関数によって変換する非線形関数手段,上記ディレイ手段の他のものから得られる信号を所定係数倍する係数手段,上記非線形関数手段および係数手段から得られる信号を加管する加管手段。ならび

4

に動作開始時に上記ディレイ手段,または上記非線形関数手段および係数手段,または上記加算手段に初期値を与える初期化手段を備え,上記加算手段の出力が最前段の上記ディレイ手段にフィードバックされるように構成されているものである。

【0009】このカオス的信号発生装置はハードウェア・アーキテクチャによって,またはコンピュータ・ソフトウェアによって実現することができる。

【0010】ハードウェア回路によって実現される第1の発明によるカオス・ディバイスは,入力信号を微小時 10間ずつ順次遅延させる複数のディレイ回路,上記ディレイ回路のうちの少なくとも1つから得られる信号を非線形関数によって変換する非線形関数回路,上記ディレイ回路の他のものから得られる信号を所定係数倍する係数回路,上記非線形関数回路および係数回路から得られる信号を加算する加算回路,ならびに動作開始時に上記ディレイ回路,または上記加算回路に初期値を与える初期化回路を備え,上記加算回路の出力が最前段の上記ディレイ回路にフィードバックされるように構成されているものであ 20る。

【0011】第1の発明によるカオス的信号発生方法は,順次与えられる複数個の信号をその順序に保存しておき,保存されている信号のうちの少なくとも1つを非線形関数によって変換し,保存されている信号の他のものを所定係数倍された信号を加算し,加算により得られた信号を最新の信号として保存しかつ保存されている信号を順次シフトするものであり,これらの一連の処理が初期値を与えることにより開始されかつ繰返されることにより30カオス的信号が得られる。

【 0 0 1 2 】第 2 の発明は複数の非線形関数要素を含むより一般的なカオス的信号発生装置(またはカオス・ディバイス)および方法を提供するものである。

【0013】第2の発明によるカオス的信号発生装置は、入力信号を所定時間ずつ順次遅延させる複数のディレイ手段、上記ディレイ手段から得られる信号をそれぞれ所定の非線形関数によって変換する複数の非線形関数手段、上記複数の非線形関数手段から得られる信号を加算する加算手段、ならびに動作開始時に上記ディレイ手40段または上記非線形関数手段にそれぞれ初期値を与える初期化手段を備え、上記加算手段の出力が最前段の上記ディレイ手段にフィードバックされるように構成されているものである。

【 0 0 1 4 】このカオス的信号発生装置も,ハードウェアによる回路またはプログラムされたコンピュータによって実現できる。

【0015】特にハードウェアによって実現される第2 の発明によるカオス・ディバイスは,入力信号を微小時間ずつ順次遅延させる複数のディレイ回路,上記ディレ 50 6

イ回路から得られる信号をそれぞれ所定の非線形関数によって変換する複数の非線形関数回路,上記複数の非線 形関数回路から得られる信号を加算する加算回路,ならびに動作開始時に上記ディレイ回路または上記非線形関数回路にそれぞれ初期値を与える初期化回路を備え,上記加算回路の出力が最前段の上記ディレイ回路にフィードバックされるように構成されているものである。

【0016】第2の発明によるカオス的信号発生方法は,順次与えられる複数個の信号をその順序に保存しておき,保存されている信号をそれぞれ所定の非線形関数によって変換し,非線形関数変換された信号を加算し,加算により得られた信号を最新の信号として保存しかつ保存されている信号を順次シフトする一連の処理を行なうものであり,この一連の処理は初期値を与えることにより開始される。そして,この一連の処理が繰返されることによりカオス的信号が得られる。

【0017】第3の発明は,多変数非線形関数要素を含む一般化されたカオス的信号発生装置および方法を提供している。

【0018】第3の発明によるカオス的信号発生装置は、複数の入力変数信号をそれぞれ所定時間遅延させる複数のディレイ手段、上記複数のディレイ手段から得られる複数の変数信号のうちの少なくとも1つをそれぞれ入力とし、この入力変数信号を1変数または多変数非線形関数により関数信号に変換する複数の非線形関数手段、ならびに各入力変数信号の初期値を与える複数の初期化手段を備え、上記非線形関数手段から得られる関数信号が対応する上記ディレイ手段にフィードバックされるように構成されているものである。

) 【 0 0 1 9 】このカオス的信号発生装置もまたハードウェア・アーキテクチャまたはコンピュータ・ソフトウェアにより実現することができる。

【0020】第3の発明によるカオス的信号発生方法は、複数の入力変数信号をそれぞれ保存しておき、保存されている複数の変数信号のうちのいくつかを複数の異なる多変数非線形関数によりそれぞれ関数信号に変換し、多変数非線形関数変換により得られた複数の関数信号を新たな入力変数信号としてそれぞれ保存する一連の処理を行なうものであり、この一連の処理は初期値を与えることにより開始される。またこの一連の処理が繰返されることにより複数のカオス的信号が得られる。この発明はさらに、第1の発明によるカオス的信号発生装置またはカオス・ディバイスにおいて用いられる線形ディレイ素子を提供している。

【 0 0 2 1 】この線形ディレイ素子は,入力信号を所定時間遅延させるディレイ要素,上記ディレイ要素から得られる信号を所定係数倍する係数要素,および上記ディレイ要素または係数要素に初期値を与える初期化要素を備えている。

【0022】この発明は,第1および第2の発明による

カオス的信号発生装置またはカオス・ディバイスで用いられる非線形ディレイ素子を提供している。

【 0 0 2 3 】この非線形ディレイ素子は,入力信号を所定時間遅延させるディレイ要素,上記ディレイ要素から得られる信号を非線形関数によって変換する非線形関数要素,および上記ディレイ要素の入力信号として,上記非線形関数要素の入力信号として,または上記非線形関数要素の出力信号として初期値を与える初期化要素を備えている。

【0024】このような線形ディレイ素子および非線形 10 ディレイ素子,ならびに加算回路を組合せることにより,第1または第2の発明によるカオス的信号発生装置またはカオス・ディバイスを構成することができる。とくに,カオス・ディバイスをIC化するときにこれらのディレイ素子は有効に使用される。

【0025】さらに、この発明は、第3の発明によるカオス的信号発生装置において用いられる一般的非線形ディレイ素子を提供している。

【 0 0 2 6 】この一般的非線形ディレイ素子は,入力変数信号を所定時間遅延させるディレイ要素,上記ディレ 20 イ要素から得られる変数信号および外部から与えられる変数信号を多変数非線形関数によって関数信号に変換する多変数非線形関数要素,ならびに上記ディレイ要素または多変数非線形関数要素に初期値を与える初期化要素を備えている。

【0027】このような一般的非線形ディレイ素子を複数個組合わせることにより,第3の発明によるカオス的信号発生装置を容易に構築することができる。

【0028】この発明によるカオス的信号発生装置(またはカオス・ディバイス)および方法によると,時間軸 30上でカオス的なふるまいをする出力信号を得ることができる。したがって,非線形関数とそのパラメータおよび初期値とに応じてカオス的出力信号がどのようなふるまいをするか等の実証的研究,理論の検証等を行なうことができるようになる。とくにこの発明によるカオス的信号発生装置をハードウェア回路により実現した場合には,きわめて高速にカオス的信号を得ることができる。

【0029】また,この発明によるカオス的信号発生装置および方法によって得られるカオス的出力信号を直接的または間接的に用いることによって種々の表示を行な 40うことができる。この表示は非予測的であり,しかも雑音とは異なるので,見ていて飽きることがなくかつ魅力的なものとなる。

【0030】この発明によるカオス的信号発生装置および方法により得られるカオス的出力信号は上記以外に, 音の発生, パターン絵の発生, 色の発生, 自然感にあふれた室内風の発生(たとえば, 扇風機の制御, 空調器の制御等), ゲーム機の制御, 噴水等における水の流れの制御等々多くの応用に利用することが可能である。

[0031]

【実施例の説明】非線形関数を含む差分方程式(または 漸化式)の解の軌道は,パラメータおよび初期値を適当 に定めることにより,カオス的ふるまいをすることが知 られている。

【0032】最も単純な差分方程式を考える。

[0033]

ここで $f(x_n)$ は,たとえば $b(x_n)^2$ 等の非線形関数を表わす。係数a,bをパラメータという。

【 0 0 3 4 】式 1 および式 2 の解は初期値 ( x 。 , y 。 ) ( n = 0 のときの x , y の値 ) を与えることにより一義的に定まる。

【 0 0 3 5 】 一般には n は時間軸上にとられ,ある有限の時間 t (一般には微小時間)ごとにインクレメントされていく。

【 0 0 3 6 】したがって,式1および式2の解(x,,, y,)をXY直交座標上に表わすことができ,解を表わ す点(x,,y,)は時間の経過にともない軌跡を描 く。

【0037】nを増大していったときに,解は一点に収束していくか,発散するか,周期性を示すか,または全く不規則に変化する。第4番目の全く不規則に変化するふるまいが一般にカオスと呼ばれている。解がどのようなふるまいをするかは,専らパラメータa,f(x)の非線形性を特定するパラメータ(たとえば,上記bなど)および初期値(xo,yo)により決定される。

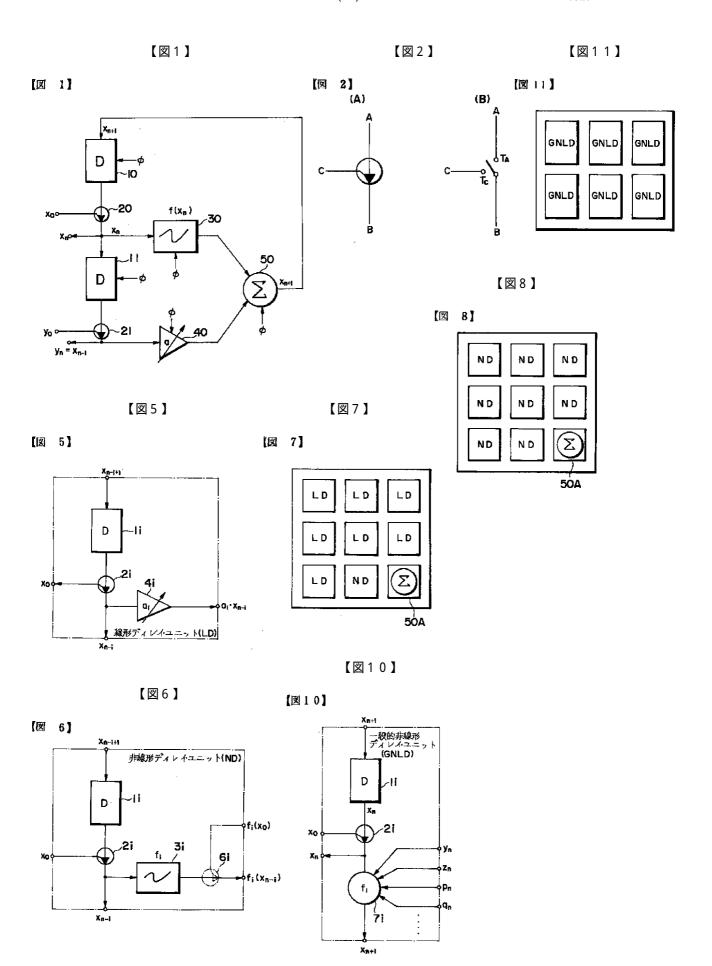

【0038】図1は式1および式2を解いて一連の解を時間の経過とともに出力するカオス的信号発生装置の機能的構成を示すものである。

【0039】このカオス的信号発生装置は,2つのディレイ要素(たとえばディレイ回路)10,11,2つの初期化要素(たとえば初期化のためのスイッチ回路)20,21,非線形関数要素(たとえば非線形関数回路)30,係数要素(たとえば係数器)40および加算要素(たとえば加算回路)50から構成されている。これらの各要素には

tの周期をもつクロック信号 が与えられ,このクロック信号 に同期して動作する。

【 0 0 4 0 】ディレイ要素10,11は,入力信号を1クロック周期 t遅延させて出力するものである。

【 0 0 4 1 】初期化要素20,21は図 2 (A) に拡大して示すシンボルによって表現され,電子回路においては具体的には図 2 (B) に示す切替スイッチによって実現される。

【 0 0 4 2 】初期値x。またはy。を与えるときには切替スイッチは端子T。に接続され,入力端子C に入力する初期値が出力端子B に伝えられる。それ以降は,切替スイッチは端子T》に接続され,入力端子A の入力が出

50 力端子Bに伝達される。

【0043】非線形関数要素30は,入力xnの非線形関 数f(x<sub>n</sub>)を出力する。

【0044】係数要素40は入力 y 。 を係数 a 倍して出力 する。

【0045】加算要素50はそのすべての入力の和を演算 し,この加算結果を x n+1 として出力する。

【0046】図1に示す構成は次のように動作する。

【0047】初期値x。,y。が与えられると,これら の初期値x。,y。は初期化要素20,21をそれぞれ通 11に,初期値 v。は係数要素40にそれぞれ与えられる。 非線形関数要素30からf(x<sub>0</sub>)が,係数要素40からa ∨。がそれぞれ出力され,加算要素50から式1にしたが って,  $x_1 = f(x_0) + a y_0$  が出力される。この値 x1 はディレイ要素10に入力する。

【0048】1クロック周期 tが経過すると,ディレ イ要素10,11からはそれぞれ x₁, x₀(= y₁)が出 力される。

\*【0049】一般にある時点でディレイ要素10,11から x n , x n-1 ( = y n ) がそれぞれ出力され,非線形関 数要素30,係数要素40および加算要素50によって式1の 演算が行なわれ,加算要素50から次の時刻の×の値× n+1 が出力され,これがディレイ要素10に与えられる。 【0050】解(x,,y,)を表わす出力は,ディレ イ要素10,11の出力端子に現われるが,これは切替スイ ッチが端子 TAに接続された初期化要素20,21の出力と して外部に取出される。

10

り,初期値x。は非線形関数要素30およびディレイ要素 10 【0051】図1の機能的構成は,後に示すように電子 回路、またはプログラムされたコンピュータによって実 現される。電子回路で実現される場合には,図2(B)に 示す切替スイッチおよび後述する各種スイッチは半導体 スイッチング素子によって好適に実現されよう。

> 【0052】次により一般的な形態について言及する。 【0053】高次の微分方程式を漸化式で表わすと式3 のようになる。

[0054]

$$x_{n+1} = f(x_n) + a_1 x_{n-1} + a_2 x_{n-2} + a_3 x_{n-3} + a_4 x_{n-4} + \dots + a_i x_{n-i} + \dots$$

式3を次のように変形する。

$q_{n+1} = p_n \quad (= x_{n-3})$

[0055]

$X_{n+1} = f(X_n) + a_1 y_n + a_2 z_n + a_3 p_n + a_4 q_n + ...$   $\vec{x}_4$ 式 5 f (xn) は非線形関数, a (i = 1, 2, 3, 4,  $y_{n+1} = x_n$  $Z_{n+1} = V_n (= X_{n-1})$ ...) は結合パラメータである。 式 7  $p_{n+1} = z_n (= x_{n-2})$

【0056】ベクトルXn+1 (ベクトルは大文字で表わ す)を,

$X_{n+1} = \{ x_{n+1} , y_{n+1} , z_{n+1} , p_{n+1} , q_{n+1} , ... \}^{\top}$   $\vec{\pi} 9$ と置くと,式4~式8は次のように表現される。 【数1】

[0057]

$$X_{n+1} = \begin{bmatrix} x_{n+1} \\ y_{n+1} \\ z_{n+1} \\ p_{n+1} \\ q_{n+1} \\ \vdots \end{bmatrix} = \begin{bmatrix} f(x_n) \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix} + \begin{bmatrix} 0 & a_1 & a_2 & a_3 & a_4 & \cdots \\ 1 & 0 & 0 & 0 & 0 & \cdots \\ 0 & 1 & 0 & 0 & 0 & \cdots \\ 0 & 0 & 1 & 0 & 0 & \cdots \\ 0 & 0 & 0 & 1 & 0 & \cdots \\ 0 & 0 & 0 & 1 & 0 & \cdots \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \end{bmatrix} \begin{bmatrix} x_n \\ y_n \\ z_n \\ p_n \\ q_n \\ \vdots \end{bmatrix}$$

…式10

ここで,

$F(x_n) = \{ f(x_n), 0, 0, 0, 0... \}^{T}$  $A = \begin{bmatrix} 0 & a_1 & a_2 & a_3 & a_4 \\ 1 & 0 & 0 & 0 & 0 & \cdots \\ 0 & 1 & 0 & 0 & 0 & \cdots \\ 0 & 0 & 1 & 0 & 0 & \cdots \\ 0 & 0 & 0 & 1 & 0 & \cdots \\ & & & \vdots & \vdots & \vdots & \ddots \end{bmatrix}$ 【数2】

$X_n = \{ x_n, y_n, z_n, p_n, q_n, ... \}^{\top}$ 式13

と置くと,式10は次のように簡潔に表現される。

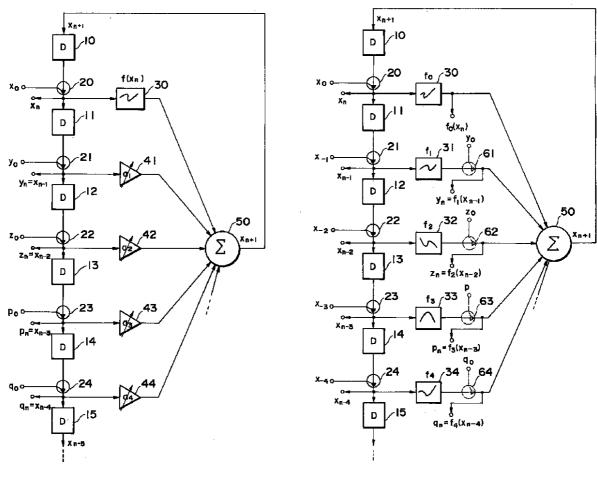

$[0058]X_{n+1} = F(x_n) + A \cdot X_n$ 式14 式3,または式4~式8,または式10,または式14で表 わされる漸化式の解X。 = { x 。 , y 。 , z 。 , p 。 , q , , ... } (式13) を求めるためのカオス的信号発生 装置の機能的構成が図3に示されている。

【0059】この機能的構成は,多数段のディレイ要素 10,11,12,13,14,…と,これらのディレイ要素間に 設けられた初期化要素20,21,22,23,24,...と,初期 化要素20の出力を入力とする非線形関数要素30と,他の 初期化要素21,22,23,24,…の出力をそれぞれ係数 a 1 , a2 , a3 , a4 , ...倍する係数要素41,42,43, 44,...と,非線形関数要素30および係数要素41,42,4 3,44,…の出力を加算する加算要素50とから構成され ている。加算要素50の出力は最前段のディレイ要素10に フィードバックされる。

【0060】初期値X。={xo,yo,zo,po, q₀ , ... } が初期化要素20,21,22,23,24,...を通 して与えられると,非線形関数要素30,係数要素41,4 2,43,44,...からそれぞれf(x<sub>0</sub>),a<sub>1</sub>y<sub>0</sub>,a 2 Z<sub>0</sub> , a<sub>3</sub> p<sub>0</sub> , a<sub>4</sub> q<sub>0</sub> , ...が出力され, これらが 加算要素50で加算されることにより, x<sub>1</sub> が得られる。 この出力 x1 はディレイ要素10にフィードバックされ

【0061】ある時刻においては,非線形関数要素30, 係数要素41,42,43,44,…にそれぞれx<sup>n</sup>,y<sup>n</sup>=x  $_{n-1}$  ,  $Z_n = X_{n-2}$  ,  $p_n = X_{n-3}$  ,  $q_n = X_{n-4}$  , ... がそれぞれ与えられ,非線形関数要素30,係数要素41, 42,43,44,…からそれぞれf(x<sub>n</sub>),a<sub>1</sub>y<sub>n</sub>,a\*30

$$X_{n+1} = f_0 (X_n) + f_1 (X_{n-1}) + f_2 (X_{n-2}) + f_3 (X_{n-3}) + f_4 (X_{n-4}) + ...$$

$\pm 15$

式15は次のように変形できる。

$x_{n+1} = f_0 (x_n) + y_n + z_n + p_n + q_n + ...$

$y_n = f_1 (x_{n-1})$ 式17 式18

$z_n = f_2 (x_{n-2})$  $p_n = f_3 (x_{n-3})$ 式19

$q_n = f_4 (x_{n-4})$ 式20

式15, または式16~式20で表わされる漸化式の解x。, または一組の $\mathbf{m} \times \mathbf{n}$  ,  $\mathbf{x}_{n-1}$  ,  $\mathbf{x}_{n-2}$  ,  $\mathbf{x}_{n-3}$  ,  $x_{n-4}$  ,...,  $\pm U \leqslant L x_n$  ,  $y_n$  ,  $z_n$  ,  $p_n$  ,  $q_n$  , …を求めるためのカオス的信号発生装置の機能的構成が 図4に示されている。この機能的構成は,多数段のディ レイ要素10,11,12,13,14,...と,これらのディレイ 要素間に設けられた初期化要素20,21,22,23,24,... と,これらの初期化要素20,21,22,23,24の出力を入 力とする非線形関数要素30,31,32,33,34,...と,こ れらの非線形関数要素30,31,32,33,34,…の出力を 加算する加算要素50とから構成されている。加算要素50 50 れ f  $_0$  (  $x_n$  ) ,  $y_n$  = f  $_1$  (  $x_{n-1}$  ) ,  $z_n$  = f

\*<sub>2</sub> z<sub>n</sub> , a<sub>3</sub> p<sub>n</sub> , a<sub>4</sub> q<sub>n</sub> , ...が得られるので , 加算 要素50からは式4で表わされる出力xmi が得られ,こ れが最前段のディレイ要素10にフィードバックされる。 【0062】図3には図示が省略されているクロック信 号 の1周期 tごとにnがインクレメントされながら 上記動作が行なわれるのはいうまでもない。

12

【0063】一組の解Xn = { xn , yn , zn , p。, q。, … } ' は, ディレイ要素10, 11, 12, 13, 14,…の出力に現われるが,これらは,切替スイッチが 端子 T A に接続された初期化要素20,21,22,23,24, ...の出力として外部に取出される。

【0064】初期化要素を通して一組の初期値X。= { x 。 , y 。 , z 。 , p 。 , q 。 , ... } <sup>T</sup> を与えること に代えて,ディレイ要素10または初期化要素20を通し て, X<sub>0</sub>, X<sub>1</sub>, X<sub>2</sub>, X<sub>3</sub>, X<sub>4</sub>,...(または,..., X-4 , X-3 , X-2 , X-1 , X<sub>0</sub> )を1クロック周期ごと に順次入力するようにしてもよい。この場合には,すべ ての初期値の入力が完了するまで加算要素50の出力をデ ィレイ要素10にフィードバックしないようにする。

【0065】図1および図3において,係数要素40,4 1,42,43,44,...の係数 a, a, , a, , a, , a, , a₄ , ...は外部から変えることができるようにしておく ことが好ましい。また,後述するように,非線形関数要 素30に設定される非線形関数の形も外部から変えること ができるようにするとよい。

【0066】続いて複数の非線形関数をもつより一般的 な漸化式について検討する。

[0067]

式15

[0068]

の出力 x mi が最前段のディレイ要素10にフィードバッ クされる。非線形関数要素30,31,32,33,34,…には 非線形関数 f<sub>0</sub> , f<sub>1</sub> , f<sub>2</sub> , f<sub>3</sub> , f<sub>4</sub> , ...がそれぞ れ設定されている。

式16

【0069】初期値x。, x-1, x-2, x-3, x-4,... 40 が初期化要素20,21,22,23,24,...を通して与えられ ると,非線形関数要素30,31,32,33,34...からそれぞ  $hf_0(x_0), y_0 = f_1(x_{-1}), z_0 = f_2(x_{-1})$ -2 ),  $p_0 = f_3$  (  $x_{-3}$  ),  $q_0 = f_4$  (  $x_{-4}$  ), ...  $\hbar$ 出力され,これらが加算要素50で加算されることによ り, x₁ が得られる。この出力 x₁ はディレイ要素10に フィードバックされる。ある時刻においては,非線形関 数要素30,31,32,33,34,…にそれぞれx。,

X n-1 , X n-2 , X n-3 , X n-4 , ...がそれぞれ与えら れ,非線形関数要素30,31,32,33,34,...からそれぞ  $_{2}$  (  $x_{n-2}$  ) ,  $p_{n} = f_{3}$  (  $x_{n-3}$  ) ,  $q_{n} = f_{4}$  ( xn-4 ) , ...が得られるので , 加算要素50からは式15また は式16で表わされる出力 x mi が得られ,これがディレ イ要素10にフィードバックされる。

【0070】図4にも図示が省略されているクロック信 号 の1周期 tごとにnがインクレメントされながら 上記動作が行なわれるのはいうまでもない。

【0071】出力 X n , X n-1 , X n-2 , X n-3 n-4 , ...はそれぞれディレイ要素10,11,12,13,14, …の出力に現われるが,これらは,切替スイッチが端子 TA に接続された初期化要素20,21,22,23,24,...の 出力として外部に取出される。また,非線形関数要素3 0,31,32,33,34,…から出力f。(x<sub>n</sub>),y<sub>n</sub> =  $f_1(x_{n-1}), z_n = f_2(x_{n-2}), p_n = f$ 3 (X<sub>n-3</sub> ), q<sub>n</sub> = f<sub>4</sub> (X<sub>n-4</sub> ),...を得ることも できる。

【0072】初期化要素21,22,23,24,…に代えて, 鎖線で示すように,非線形関数要素31,32,33,34,... の出力側(加算要素50の対応する入力側)に初期値y。  $= f_1 (X_{-1}), Z_0 = f_2 (X_{-2}), p_0 = f_3 (X_{-2})$ 3), q<sub>0</sub> = f<sub>4</sub> (x<sub>4</sub>),…をそれぞれ初期化要素6 1,62,63,64,...を通して入力するようにすることも できる。

【0073】図4においても,非線形関数要素30,31, 32,33,34,…に設定される非線形関数は可変であるこ とが好ましい。

【0074】図3に示す構成は,電子回路上いくつかの ユニットに分解して考えることができる。図3に示す構 成の単位となるユニットが図5および図6に示されてい る。図5の回路を線形ディレイ・ユニット(LD=Line 30 ar Delay Unit )と呼ぶ。この線形ディレイ・ユニット (LD)は,ディレイ要素1i,初期化要素2iおよび係数 要素4i(i=1,2,3,4,...)を含み,ディレイ要素1iの出力 側に初期化要素2iが,さらに初期化要素2iの出力側に係 数要素4iがそれぞれ接続されている。線形ディレイ・ユ ニット(LD)には,ディレイ要素1iに与える入力x の入力端子,ディレイ要素1iの出力 x 🛶 を初期 化要素2iを通して取出す出力端子,初期値x。(または y。 , z。 , p。 , q。等)の入力端子 , および係数要 素4iの出力a: ・x:: を取出す修飾出力端子がさらに 40 ニット間の結線のため配線パターンの図示が省略されて 設けられている。

【0075】図6の回路を非線形ディレイ・ユニット (ND=Nonlinear Delay Unit)と呼ぶ。この非線形デ ィレイ・ユニット(ND)は,ディレイ要素1i,初期化\* \*要素2iおよび非線形関数要素3i(i=0,1,2,3,4,...)を含 み,ディレイ要素1iの出力側に初期化要素2iが,初期化 要素2iの出力側に非線形関数要素3iがそれぞれ接続され ている。非線形ディレイ・ユニット(ND)には,ディ レイ要素1iに与える入力 x n-i+1 の入力端子, ディレイ 要素1iの出力 x ... を初期化要素2iを通して取出す出力 端子,非線形関数要素3iの出力f:(x<sub>n-i</sub>)を取出す 修飾出力端子および,初期値x。(またはx1,x2,

×₃,×₄等)の入力端子が設けられている。

14

【0076】要すれば,鎖線で示すように,非線形関数 要素3iの出力側に初期化要素6i(i=1,2,3,4,...)を設 け,かつ初期値f:(xn)の入力端子を設ける。 【0077】1個の非線形ディレイ・ユニット(ND) と、複数個の線形ディレイ・ユニット(LD)の各入出 力間を縦続接続し,かつ各ユニット(ND),(LD) の出力 f i ( x n-i ) , a i ・ x n-i が加算要素50に入 力するように接続し,加算要素50の出力を非線形ディレ イ・ユニット(ND)にフィードバックすることによ リ,図3に示す回路が構成される。

【0078】このような非線形ディレイ・ユニット(N D)と,複数個の線形ディレイ・ユニット(LD)と, 加算要素50を含む加算ユニット50Aとを1チップ上にI C化することが可能である。このようにIC化されたカ オス・ディバイスのチップ・レイアウトの概要が図7に 示されている。このレイアウトではユニット間の結線の ための配線パターンの図示が省略されている。加算ユニ ット50Aは演算増幅器とその入力抵抗アレイとから構成 されよう。

【0079】同じように、複数個の非線形ディレイ・ユ ニット(ND)の各入出力間を縦続接続し,かつ各ユニ ット(ND)の出力 f: (x<sub>n-i</sub> )が加算要素50に入力 するように接続し,加算要素50の出力を最前段の非線形 ディレイ・ユニット(ND)にフィードバックすること により,図4に示す回路が構成される。

【0080】このような複数個の非線形ディレイ・ユニ ット(ND)と,加算要素50を含む加算ユニット50Aと を1チップ上にIC化することが可能である。このよう にIC化されたカオス・ディバイスのチップ・レイアウ トの概要が図8に示されている。このレイアウトでもユ

【0081】一般的な漸化式は次のように表わされる。 [0082]

$x_{n+1} = f_1 (x_n, y_n, z_n, p_n, q_n, ...)$ 式21  $y_{n+1} = f_2 (x_n, y_n, z_n, p_n, q_n, ...)$ 式22  $z_{n+1} = f_3 (x_n, y_n, z_n, p_n, q_n, ...)$ 式23  $p_{n+1} = f_4 (x_n, y_n, z_n, p_n, q_n, ...)$ 式24  $q_{n+1} = f_5 (x_n, y_n, z_n, p_n, q_n, ...)$ 式25

f<sub>1</sub> , f<sub>2</sub> , f<sub>3</sub> , f<sub>4</sub> , f<sub>5</sub> , ... は多変数の非線形関数である。

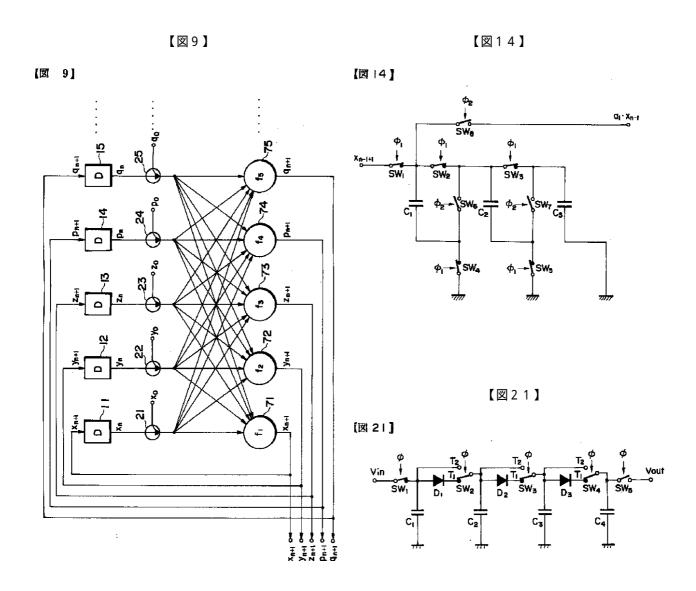

【0083】式21~式25で表わされる漸化式の一連の解を発生するカオス的信号発生装置の機能的構成が図9に示されている。式21~式25のそれぞれについてディレイ要素11~15,初期化要素21~25および多変数非線形関数要素71~75がそれぞれ,縦続接続されている。各多変数非線形関数要素71~75には,すべての初期化要素21~25の出力が与えられる。多変数非線形関数要素の出力× 対応するディレイ要素11~15にそれぞれフィードバックされる。多変数非線形関数要素には,必ずしもすべての初期化要素の出力を与えなくてもよい。多変数非線形関数要素として,重み付き加算と閾値関数を用いた特殊な場合がホップ・フィールド・モデルである。

【0084】図9に示す構成は、図10に示す一般的非線 形ディレイ・ユニット(GNLD=Generalized Nonlin ear Delay Unit)を組合せることにより構築することが できる。複数個の一般的非線形ディレイ・ユニット(G NLD)からなるカオス・ディバイスのICチップ・レ 20 イアウトが図11に示されている。このレイアウトではユ ニット間の結線のための配線パターンの図示が省略され ている。

【 0 0 8 5 】続いて上述した線形ディレイ・ユニット ( L D ) および非線形ディレイ・ユニット( N D ) を電 子回路により実現した具体例について述べる。

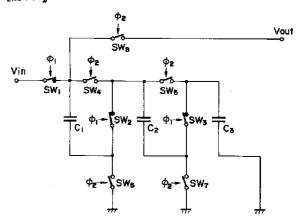

【0086】図12は線形ディレイ・ユニット(LD)の 具体的回路を示している。この図において,図5との対 応関係を分りやすくするために,入,出力信号について は図5に示すものと同一符号が使用されている。

【0087】ディレイ要素は2つのコンデンサC+,C2と切替スイッチSW+,SW2とから構成されている。切替スイッチSW+,SW2は図13に示すようなクロック信号によって切替制御される。ディレイ時間 tはクロック信号の1周期に等しい。係数要素はフィードバック抵抗R+を含む演算増幅器A+によって実現される。係数a+は抵抗R+の値によって調整される。初期化要素はスイッチSW3を含む。

【  $0 \ 0 \ 8 \ 8$  】切替スイッチSW1 が端子  $T_2$  に 、切替ス 力信号  $V_1$  が  $3 \ 2 \ 3$  へッチSW2 が端子  $T_1$  にそれぞれ接続され 、スイッチ  $40 \ 3$  ることになる。 S  $W_3$  がオンとされることにより初期値  $X_0$  が入力され  $X_0$  で を表わす電圧信号によって入力コン じように表現をデンサ  $X_1$  に充電される。コンデンサ  $X_2$  の電圧は反転 カ信号  $X_1$  で  $X_2$  の電子  $X_3$  の電子  $X_4$  の  $X_$

【 0 0 8 9 】次に,切替スイッチ S  $W_1$  が端子  $T_1$  に,切替スイッチ S  $W_2$  が端子  $T_2$  に接続されると,入力コンデンサ  $C_1$  には入力  $X_{n-i+1}$  を表わす電圧が蓄えられ,一方出力コンデンサ  $C_2$  の電圧は反転増幅器  $A_{12}$  を経て出力  $a_1$  ・  $x_{n-i}$  として出力される。

16

【 0 0 9 0 】再び切替スイッチS  $W_1$  が端子 $T_2$  に ,切替スイッチS  $W_2$  が端子 $T_1$  に接続されると , 入力コンデンサ $C_1$  の電圧が -  $a_1$  倍されて出力コンデンサ $C_2$  に蓄えられることになる。このようにして , 時間 t ごとに入力が取込まれかつ出力が外部に取出されることになる。

【0091】上述したように切替スイッチSW, ,SW , スイッチSW。は半導体スイッチング回路により実現されよう。スイッチSW。は手動により直接にまたは間接に操作または制御されよう。このような線形ディレイ・ユニット内または線形ディレイ・ユニット間には適宜バッファ回路が接続されよう。

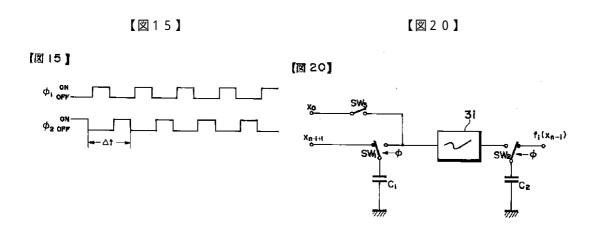

【0092】図14は線形ディレイ・ユニット(LD)の 具体例の他の構成を示している。この図および後に言及 する各図においても、図12に示すスイッチやコンデンサ と同じ符号SW1、SW2、...、C1、C2、...等が使 用されているが、煩雑さを避けるために便宜的に符号を 重複して使用しているにすぎず、各符号は各図ごとに相 互に独立である。

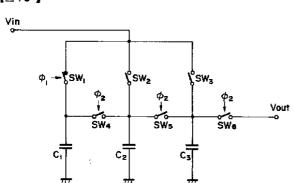

【0093】図14に示す回路は、複数の(図14では3個の)コンデンサC₁、C₂、C₃と複数のスイッチSW₁~SW₅はクロック信号 ₁によって、スイッチSW₅~SW₅はクロック信号 ₂によってそれぞれ制御される。クロック信号 ₁と ₂は図15に示すように逆位相の信号である。

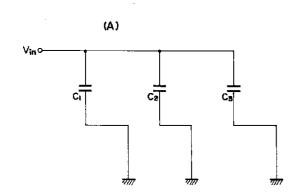

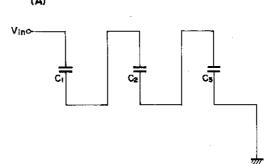

【 0 0 9 4 】クロック信号 、によってスイッチ S W<sub>1</sub> ~ S W<sub>2</sub> がオンとされたときに,スイッチ S W<sub>3</sub> ~ S W はオフ状態を保つ。このときに形成される回路が図16 (A)に示されている。 3 個のコンデンサ C<sub>1</sub> , C<sub>2</sub> , C<sub>3</sub> が並列に接続され,これらのコンデンサは入力電圧信号 V<sub>10</sub> によって等しい電圧に充電される。

【 0 0 9 6 】以下の説明においては,図16で示したと同じように表現を簡略化するために入力信号  $x_{n-i}$  に代えて入力信号  $v_{in}$  の符号を,出力信号  $x_{n-i}$  に代えて出力信号  $v_{out}$  の符号をそれぞれ用いることにする。

【 0 0 9 7 】図14において,スイッチS  $W_2$  ~ S  $W_7$  を選択的にオン,オフ制御するようにすると,係数要素の係数  $a_1$  を変えることができる。

【 0 0 9 8 】コンデンサ $C_1 \sim C_3$  に充電するときには図16(A) に示すようにスイッチ $SW_1 \sim SW_3$  をオン、 $SW_6 \sim SW_8$  をオフとする。

【0099】次にコンデンサC1~C3に充電された電 荷による出力 V out を取出すときには,スイッチS  $W_{\epsilon}$  ,  $SW_{\epsilon}$  をオンとし ,  $ZAY + SW_{\tau}$  をオフのまま に保つ。またスイッチSW1 , SW2 , SW4 をオフと し,スイッチSW。,SW。をオンのままに保つ。する と,コンデンサC2とC3が並列に接続された状態に保 たれ,出力 v 。 は2 v in の値を示す。これらのスイッ チSW<sub>1</sub> ~ SW<sub>8</sub> の操作により, V<sub>out</sub> = V<sub>in</sub> の値をも つ出力を得ることもできる。

のいずれか一方または両方を常時オン状態としておくこ とにより,スイッチSW。およびSW, のうちの対応す るいずれか一方または両方がオンとなったときに、コン デンサC4 , C2 に充電されていた電荷は放電するの で,出力電圧 Vout を2 Vin または Vin とすることがで きる。

【0101】このように,スイッチSW₁~SW₀のオ ン,オフ制御のやり方を変えることにより所望の係数 a - を得ることができる。接続するコンデンサの数を増加 させることにより係数 a の値の選択の自由度が高ま る。IC基板上に多数のコンデンサとスイッチとをあら かじめ設けておき,これらをマスク・プログラマブルま たはフィールド・プログラマブルに構成することにより 所望の係数 a を得ることができるようになる。このこ とは,後述する多数のコンデンサを用いた他の具体的回 路にもあてはまる。

【0102】図14においては煩雑さを避けるために初期 化要素の図示が省略されているが,この初期化要素は図 12に示す考え方で付加することができる。一般に初期化 要素はスイッチと,このスイッチがオンされたときに入 30 力する初期値を表わす電圧を保持するコンデンサとによ って構成することができる。このことは,後述する他の 具体例においても全く同じである。

【0103】図14に示す回路は,並列に接続された複数 のコンデンサを入力電圧によって充電し、これらを直列 に接続することにより入力電圧よりも高い電圧の出力 (a:>1)を取出すものである。

【0104】これに対して,直列に接続された複数のコ ンデンサを入力電圧によって充電し、これらを並列に接 続することにより,入力電圧よりも低い電圧の出力(a 、 < 1)を取出すようにすることもできる。その構成の 一例が図17に示されている。

【0105】図17に示す回路は,複数の(図17では3個 の) コンデンサC1 , C2 , C3 と複数のスイッチSW\*

【 0 1 1 3 】図17においても,スイッチSW2 ~ SW7

$4 C V_{out} + 2 C V_{out} + C V_{out} = 7 C V_{out} = 3 Q$ 式31

式30と式31により,

$v_{out} = (3/7)(Q/C) = (3/7)(4/7)v_{in}$ 式32  $= (12/49) V_{in}$

を得る。

\*, ~ SW<sub>8</sub> とから構成されている。スイッチSW<sub>1</sub> ~ S W₃ はクロック信号 ₁ によって , スイッチ S W₄ ~ S W。はクロック信号 2 によってそれぞれ制御される。 クロック信号 1 と 2 は図15に示すものと同じであ

18

【 0 1 0 6 】 クロック信号 <sup>1</sup> によってスイッチ S W<sub>1</sub> ~ S W<sub>3</sub> がオンとされたときに,スイッチ S W<sub>4</sub> ~ S W 。はオフ状態を保つ。このときに形成される回路が図18 (A)に示されている。 3 個のコンデンサ C₁ , C₂ , C 【 0 1 0 0 】上記に代えて,SW〞およびSW〞のうち 10 ゜が直列に接続され,これらのコンデンサは入力電圧信 号vinによって充電される。

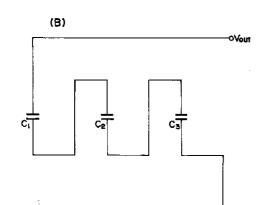

> 【0107】次にクロック信号 2 によってスイッチS  $W_4 \sim SW_8$  がオンとされると,スイッチ $SW_1 \sim SW$ ₃ はオフの状態となる。このとき形成される回路が図18 (B)に示されている。3個のコンデンサC₁ , C₂ , C ₃ は並列に接続される。したがって C₁ = C₂ = C₃ と すれば,出力信号 vωt は v in / 3 となる。すなわち, 図17に示す回路によると,入力信号 vin が 1 / 3 倍され かつ時間 t遅延されて出力されることになる。

20 【 0 1 0 8 】コンデンサ C₁ , C₂ , C₃ の値の設定の 仕方によって任意の係数 a: (a:<1)を得ることが

【 0 1 0 9 】たとえば , Cを単位容量として , C₁ = 4 C , C<sub>2</sub> = 2 C , C<sub>3</sub> = Cとする。図18(A) において各 コンデンサC1 , C2 , C3 には等しい電荷が蓄積され る。この電荷をQとする。また,各コンデンサC₁,C 2 , C₃ の両端の電圧をそれぞれ V₁ , V₂ , V₃ とす る。各コンデンサC1 , C2 , C3 において次式が成立 つ。

$[0110]Q = 4CV_1$ 式26  $Q = 2 C V_2$ 式27  $Q = C V_3$ 式28  $V_{in} = V_1 + V_2 + V_3$ 式29 これより,

$Q/C = (4/7) V_{in}$ 式30 を得る。

【0111】一方,図18(B)において,3Qの電荷が3 つのコンデンサC1 , C2 , C3 に再分配される。各コ 40 ンデンサC<sub>1</sub> , C<sub>2</sub> , C<sub>3</sub> に蓄えられる電荷量はそれぞ れ4CVout , 2CVout , CVout であるから次式が 成立つ。

[0112]

を選択的にオン,オフ制御するようにすると,係数要素 50 の係数 a: を変えることができる。

【 0 1 1 4 】図19はさらに他の例を示すものである。ここでは,入力電圧 Vin によってコンデンサ C1 , C2 , C3 のいずれか 1 つ , 2 つまたは全部に充電し , その後 , 充電されたコンデンサの電荷を 3 つのコンデンサに再分配して出力電圧 Vout として取出す。

【0115】たとえば、クロック信号 1 によってスイッチSW1のみをオンとする。他のスイッチSW2 ~ SW6 はオフに保たれる。これにより、入力電圧 Vin によってコンデンサC1 に充電される。次に、クロック信号 2 によってスイッチSW4 ~ SW6 をオンとする。他のスイッチSW1 ~ SW3 はオフの状態に保持される。すると、コンデンサC1 に充電された電荷が他のコンデンサC2 とC3 に分配され、これにしたがって定まる電圧の出力 Vout が得られる。 Vout < Vin , すなわちょ。 < 1である。

【 0 1 1 6 】スイッチSW、をオンとすることに代えて,クロック信号 、 によってスイッチSW』をオンとしてコンデンサC』に充電するようにしてもよいし,スイッチSW』をオンとしてコンデンサC。に充電するようにしてもよいし,スイッチSW』~SW。のうちの2つをオンとして対応する2つのコンデンサに充電するようにしてもよい。

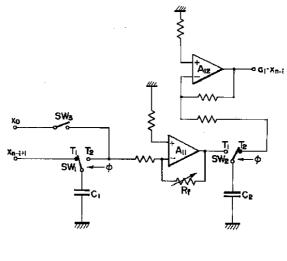

【0117】図20は非線形ディレイ・ユニット(ND)の具体例を示すものであり、図6との対応関係を明らかにするために、入、出力信号としては図6に示すものと同一符号が用いられている。非線形関数要素3iの具体例については後述する。

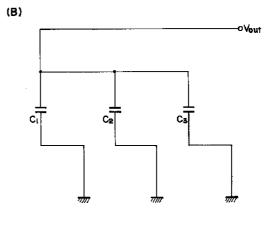

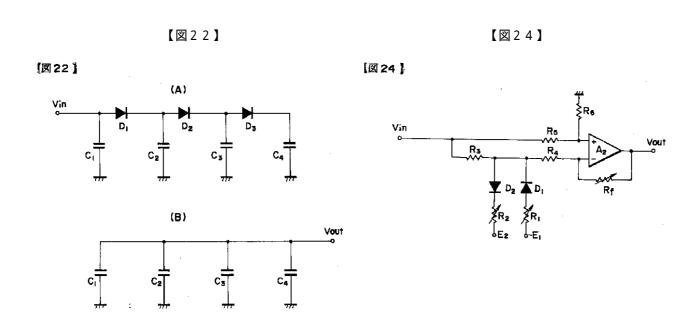

【 0 1 1 9 】 クロック信号 によって,スイッチ S  $W_1$  がオン,切替スイッチ S  $W_2$  ~ S  $W_4$  が端子  $T_1$  に接続,スイッチ S  $W_5$  がオフとされた充電状態が図22(A) に示されている。ダイオード  $D_1$  ~  $D_3$  の順方向降下電圧を  $V_0$  とする。

\*【0120】入力電圧 V in が V in V p とのときはコンデンサ C 1 にのみ充電される。 V p < V in 2 V p のときはコンデンサ C 1 と C 2 に充電される。 2 V p < V in 3 V p のときはコンデンサ C 1 と C 2 と C 3 に充電される。 3 V p < V in になるとすべてのコンデンサ C 1 ~ C 4 に充電される。このように入力電圧 V in の大きさに応じて充電されるコンデンサの数が異なる。

20

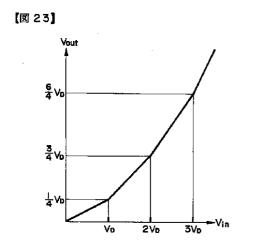

【0121】次にクロック信号 によって,スイッチSWiがオフ,切替スイッチSWi~SWiが端子Tiに10 接続,スイッチSWiがオンとされた出力電圧取出し状態が図22(B) に示されている。すべてのコンデンサCi~Ciが並列に接続され,先に充電されたコンデンサの電荷がすべてのコンデンサに分配されることになる。入力電圧 Vinの大きさに応じて充電されるコンデンサの数および電荷量が異なるから,入力電圧 Vin/出力電圧 Vin/出力電圧 Vin/が図23に示すようになる。この特性は非線形特性である。すなわち,図21に示す回路によると,入力電圧 Vin/が図23に示す非線形特性によって変換されることにより得られる出力電圧 Vout が,入力電圧 Vinの入力20 から周期 t遅れて出力されることになる。

【0122】図24は非線形関数要素3iを電子回路により具体化した一例を示すものである。この回路は,フィードバック可変抵抗 Riをもつ非反転演算増幅器 Azを含む。入力電圧 Vin は入力抵抗を介して増幅器 Azの正および負入力端子に与えられる。増幅器 Azの負入力端子は入力抵抗を介して 2 つのダイオード Di , Dz (このダイオードも図21に示すものと同じ符号が使用されているが相互に関連性はない)が並列にかつ相互に逆向きに接続されている。一方のダイオード Di のアノードには可変抵抗 Ri を介して - Ei の電圧が,他方のダイオード Dz のカソードには可変抵抗 Rzを介して + Ezの電圧がそれぞれ印加されている。出力電圧 Vout は増幅器 Azの出力端子より得られる。

【 0 1 2 3 】今 , ダイオードの順方向降下電圧 v 。 を無視して考えると , 入力電圧 v in が

【数3】

$$v_{1n} \ge \frac{(R_3 + R_4) (R_5 + R_6)}{R_4 R_5 + R_4 R_6 + R_3 R_6} E_2 \cdots$$

$\therefore$   $\therefore$

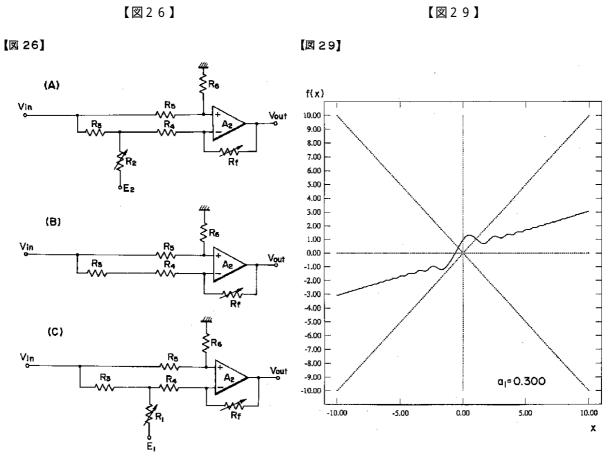

を満たす場合には,ダイオード $D_2$  のみが導通状態となり,図24の回路は図26(A) に示すようになる。この回路は正の増幅度を持ち,その増幅度は抵抗 $R_2$  および $R_4$

の少なくともいずれか一方により変えることができる。 【 0 1 2 4 】入力電圧 V in が

$$-\frac{(R_{3}+R_{4})(R_{5}+R_{6})}{R_{4}R_{5}+R_{4}R_{6}+R_{3}R_{6}}E_{1} \leq v_{in} < \frac{(R_{3}+R_{4})(R_{5}+R_{6})}{R_{4}R_{5}+R_{4}R_{6}+R_{3}R_{6}}E_{2}$$

…式34

の場合には,ダイオードD1, D2 はともに遮断状態と なるから,図24の回路は図26(B)に示すようになる。増 幅器 A₂のフィードバック抵抗 R← を適当に選ぶことに\*

\* より負の増幅度をもたせることができる。

【0125】入力電圧 Vin が

【数5】

$$v_{in} < -\frac{(R_3 + R_4) (R_5 + R_6)}{R_4 R_5 + R_4 R_6 + R_3 R_6} E_1$$

· · \$\tag{35}

の場合には,ダイオードD4のみが導通状態となるの で,図26(C)に示す回路が実現される。この回路もまた 正の増幅度をもち、その増幅度は抵抗 R および R の 10 少なくともいずれか一方によって調整することができ る。

【0126】したがって,図24に示す回路の入出力特性 は図25に図示されるように非線形性を示す。

【0127】上述した種々の電子回路はすべて電圧モー ドで動作するものである。

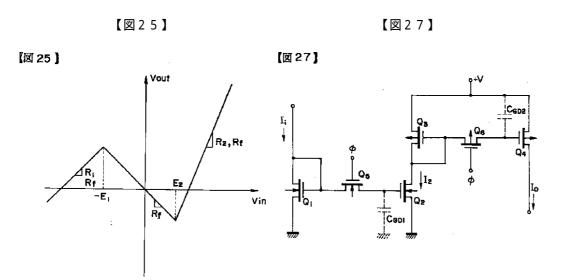

【0128】次に電流モードで動作する線形ディレイ・ ユニット(LD)および非線形ディレイ・ユニット(N D)の具体例について説明する。

【 0 1 2 9 】図27は電流モードで動作する線形ディレイ 20 Q+に入力電流 I が与えられると、これに対応した電 ・ユニット(LD)の具体的回路例を示すものである。 この回路は2つのスイッチト・カレント・ミラーによっ て構成されている。入力側のスイッチト・カレント・ミ ラーはカレント・ミラーを構成するnMOSFET Q<sub>1</sub> , Q<sub>2</sub> と , これらの F E T Q<sub>1</sub> , Q<sub>2</sub> のゲート間に 接続されたスイッチング素子としてのnMOSFETQ

$$I_2 = [(W_2 / L_2) / (W_1 / L_1)] I_1$$

このとき, FETQ2のゲート/ドレイン間寄生容量C ® に電流 I₂ に対応するゲート電圧に等しい電圧を表 わす電荷が蓄えられる。電流 I2 は F E T Q3 にも流れ FETQ3のゲート/ドレイン間には電流I2に対応す る電圧降下が発生する。

【0133】次にクロック信号 が L レベルになると F ETQ。はオフ,FETQ。はオンとなる。したがって 出力側のカレント・ミラーが動作する。すなわち、容量 Con に蓄えられた電荷による電圧によってFET

₅とから構成されている。FETQ₁に入力信号が電流 I: として与えられる。出力側のスイッチト・カレント ・ミラーはカレント・ミラーを構成するpMOSFET Q<sub>3</sub> , Q<sub>4</sub> と , これらの F E T Q<sub>3</sub> , Q<sub>4</sub> のゲート間に 接続されたスイッチング素子としてのpMOSFETQ 。とから構成されている。FETQ4から出力信号が電 流 I。として得られる。スイッチング素子としてのFE TQ。,Q。はクロック信号 (図13参照)により制御 される。

【0130】クロック信号 がHレベルのときFETQ ₅ はオン , F E T Q ₅ はオフとなる。 F E T Q ₅ がオン であるから入力側のカレント・ミラーが動作し、FET 流I2 がFETQ2 に流れる。

【 0 1 3 1 】 F E T Q₁ のチャネル幅 / チャネル長の比 (これを以下W/L比という)をW₁/L₁,FETQ 2 のW / L比をW2 / L2 とすると,電流 I2 は次式で 与えられる。

[0132]

式36

Q<sub>2</sub> , Q<sub>3</sub> に電流 I<sub>2</sub> が流れ続け,この時生じている F ETQ3のゲート/ドレイン間の電圧降下に等しい電圧 まで,オンとなったFETQ。を通じてC๑₂ が充電さ れ,その結果として出力側のFETQ4 にはこれに応じ た出力電流 I。が流れることになる。FETQ。のW/ L比をW3 / L3 , FETQ4 のW / L比をW4 / L4 とすると,出力電流 I。 は次式で与えられる。

[0134]

したがって,出力電流 I。は入力電流 I:に a:倍され た電流値をもち,かつ入力電流 I の入力時点から時間

t遅れた時点で出力されることになる。係数 a は好 ましくはW4 / L4 , W1 / L1 で調整するとよい。

【0135】このような電流モードの回路は,加算が結 線(ワイヤードサム)のみでよく,構成素子数が少なく IC化に適している。たとえば図12に示す電圧モードの 線形ディレイ・ユニットと比較してみよう。

【 0 1 3 6 】図12に示す電圧モードの線形ディレイ・ユ 50 も不要である。図27から分るようにトランジスタは6個

ニット(LD)は,抵抗素子が3個必要であり,その形 成のために大面積が必要となる。また,演算増幅器とス イッチとを含むからこれをトランジスタで実現するため には11~20個のトランジスタが必要である。また少なく とも2個の容量(コンデンサ)が必要である。

【0137】これに対して図27に示す電流モードの線形 ディレイ・ユニット(LD)では抵抗素子は不要であ り,FETのゲート容量を利用しているからコンデンサ

22

ですむ。

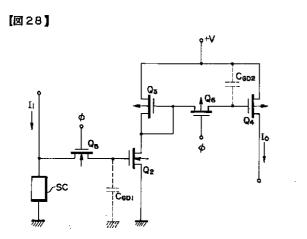

【0138】次に図28を参照して非線形ディレイ・ユニ ット(ND)を電流モードで動作する回路により実現し た具体例について説明する。

【0139】図28において図27に示すものと同一物には 同一符号が付されている。図28の回路には図27の回路と 比較すると,入力側のFETQ:が非線形機能素子SC によって置きかえられている。この非線形機能素子SC は非線形な電流/電圧特性をもつもので,たとえばサイ リスタで実現でき、ICに対して外付けしてもよいし、 ICチップ内に埋込むようにすることもできる。

【0140】入力電流 I: に対して非線形変換された電 圧を表わす電荷が容量 C 📾 に蓄えられることになるの で,図28の回路では,時間 t後に非線形変換された出 力電流 I。 が得られることになる。

【0141】最後に上述したカオス・ディバイスの応用 例について説明する。

【0142】最も簡単な図1に示す構成をコンピュータ ・ソフトウェアで実現し、これによるシュミレーション 結果について説明する。

【0143】式1および式2を次のように書きなおす。  $[0144]x_{n+1} = f(x_n) + a_2 y_n$  $y_{n+1} = x_n$ 式40

非線形関数f(xn)を次式で表わす。

[0145]

【数6】

$$f(x_n) = a_1 x + \frac{x + \cos x^2}{1 + x^2} \cdot \mathbb{R}41$$

ここで a<sub>1</sub> , a<sub>2</sub> は定数 (パラメータ) である。

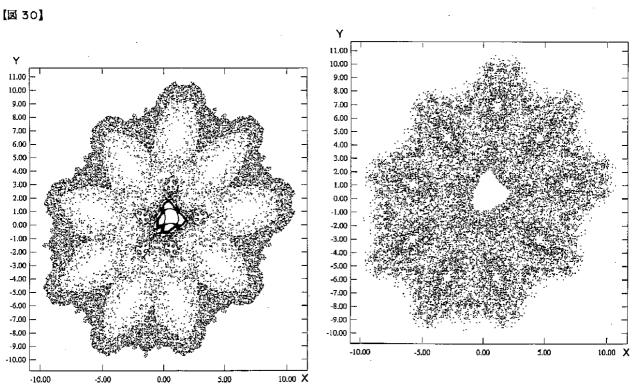

【0146】式41で表わされる非線形関数f(x)は図 29に示す曲線を描く。ここで a = 0.300 である。

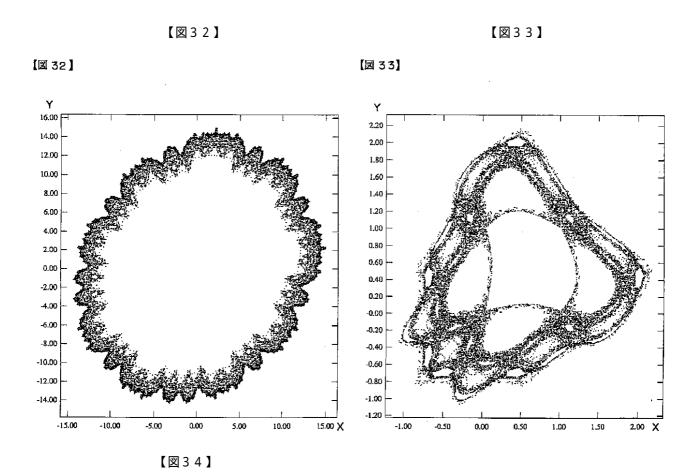

【0147】図30から図34は式39~式41から得られる (x, ,y, )によって表わされる点をXY座標に表現 したものであり, n = 1~20000 , すなわち初期値(x 。,y。)を含めて20001 個の点が表わされている。

【0148】図30は初期値x。=0.000,y。=0.000 ,パラメータa₁ = 0.300 , a₂ = -1.000 の条件を 設定した場合に得られるパターンを表わしている。

【0149】図31はパラメータ(a<sub>1</sub> = 0.300 , a<sub>2</sub> = - 1.000 )を固定し,初期値をx。= 5.000 , y。 = 5.0 00 に変化させることにより得られるパターンを示す。 初期値を変えることによって,点の集合によって表わさ れるパターン(図柄)がかなり変化することが分る。

【0150】図32はパラメータ(a1 = 0.300 , a2 = - 1.000 )を固定し,初期値をさらにx。 = 10.000, y 。 = 10.000に変化させた場合を示す。点の集合によって 表わされる図柄はさらに変貌を遂げている。

24

。 = 0.000 , y。 = 0.000 ) , 一方のパラメータを a 1 =0.290 (a2 = -1.000 は固定)とわずかに変えた場 合に得られるパターンである。図30の場合と異なり、パ ターンはおよそ - 1 x , y + 2の中に閉じ込められ ており、パラメータを少し変えただけでもパターンが大 幅に変化することが分る。

【0152】図34は一方のパラメータをa₁=1.000 に さらに変えた場合であり,初期値(x。=0.000,y。 =0.000 ) および他方のパラメータ(a2 = -1.000 ) 10 は変更していない。図柄が完全に変貌している。

【 0 1 5 3 】このような点(x , , y , ) の集合を2次 元的に表示する応用例が考えられる。表示装置として は、CRT表示装置、プラズマ・ディスプレイ、液晶表 示装置、マトリクス状に点光源を配置したもの等種々の ものを用いることができる。

【0154】表示の仕方には次の方法がある。

【0155】1)パターン形成過程の表示

一定時間ごとにnをインクレメントしながら,そのとき 得られた(x, ,y,)によって表わされる点を順次表 20 示する。既に表示した点は消してしまっても、そのまま 残してもよい。

【0156】この表示によって時間の経過にしたがって パターンが形成されていく様子, または点の軌跡が分 る。

【0157】2)静止パターンの表示

所定数 (たとえば上述した20001 個)の点の座標の集合 をあらかじめ求めておき,これらのすべての点を一挙に 表示する。図30~図34に示すようなパターンが表示され るであろう。

30 【 0 1 5 8 】 3 ) 動パターンの表示

> 2) に示す静止パターンの表示において, nをさらにイ ンクレメントして新たな点を求め、この点を追加的に表 示するとともに最も古い点の表示を消去する。表示され ている点の数は常に一定であるが,表示されているパタ ーンが時間の経過とともに変化していく。

> 【0159】4)初期値,パラメータの少なくとも1つ を変化させる。

> 【0160】この方法は上記1)~3)のすべてにあて はまる。

40 【0161】とくに2)の表示方法においては,図30の パターンから図31のパターンへ,または図32のパターン から図33のパターンへというように表示パターンが突然 変化する。

【0162】このような表示は広告の背景表示として効 果的であろう。上述したパターンの変化,点の軌跡は全 く不規則であり予測できない。しかし雑音のような不快 さもなく、見ていて飽きることがなくかつ魅力的であ る。

【0163】以上の説明は,システムのダイナミクスが 【0151】図33は初期値を図30の場合と同じとし(x 50 差分方程式(たとえば式1)で表わされる場合について

述べてきたが,

【数7】  $\mathbf{d} \mathbf{x}$ -≔ f(x) + ay ··式42

【数8】

$$\frac{d y}{d t} = x \quad \cdot : 式43$$

のような微分方程式で表わされる場合も同様であり、こ 10 の他の例を示す回路図である。 の場合はディレイ要素の代りに積分要素を用いればよ い。この発明において「ディレイ要素」,「ディレイ手 段」、「ディレイ回路」は、「積分要素」、「積分手 段」,「積分回路」を含む概念である。

### 【図面の簡単な説明】

【図1】1つの非線形関数要素と1つの係数要素とを含 む最も簡単なカオス的信号発生装置の機能的構成を示 す。

【図2】(A) は初期化要素のシンボルを , (B) は具体的 回路例をそれぞれ示す。

【図3】1つの非線形関数要素と複数の係数要素とを含 むカオス的信号発生装置の機能的構成を示す。

【図4】複数の非線形関数要素を含む一般的なカオス的 信号発生装置の機能的構成を示す。

【図5】線形ディレイ・ユニットの回路構成を示すブロ ック図である。

【図6】非線形ディレイ・ユニットの回路構成を示すブ ロック図である。

【図7】IC化されたカオス・ディバイスのレイアウト を示す。

【図8】IC化された他のカオス・ディバイスのレイア ウトを示す。

【図9】複数の多変数非線形関数要素を含む一般的な力 オス信号発生装置の機能的構成を示す。

【図10】一般的非線形ディレイ・ユニットの回路構成 を示すブロック図である。

【図11】IC化されたカオス・ディバイスのレイアウ トを示す。

【図12】線形ディレイ・ユニットの具体的回路構成を 示す回路図である。

【図13】クロック信号を示す波形図である。

【図14】線形ディレイ・ユニットの具体的回路構成の 他の例を示す回路図である。

【図15】クロック信号を示す波形図である。

【図16】(A) および(B) は図14に示す回路の動作を示 す各時点の等価回路図である。

26

【図17】線形ディレイ・ユニットの具体的回路構成の さらに他の例を示す回路図である。

【図18】(A) および(B) は図17に示す回路の動作を示 す各時点の等価回路図である。

【図19】線形ディレイ・ユニットの具体的回路構成の さらに他の例を示す回路図である。

【図20】非線形ディレイ・ユニットの具体的回路構成 を示す回路図である。

【図21】非線形ディレイ・ユニットの具体的回路構成

【図22】(A) および(B) は図21に示す回路の動作を示 す各時点の等価回路図である。

【図23】図21に示す回路の入出力特性を示すグラフで

【図24】非線形関数要素の具体例を示す回路図であ

【図25】図24に示す回路の入出力特性を示すグラフで ある。

【図26】(A),(B) および(C) は図24に示す回路の動 20 作を示す入力信号の各レンジごとの等価回路図である。

【図27】線形ディレイ・ユニットの電流モードで動作 する具体的回路構成を示す回路図である。

【図28】非線形ディレイ・ユニットの電流モードで動 作する具体的回路構成を示す回路図である。

【図29】非線形関数の特性の一例を示すグラフであ

【図30】図29に示す非線形関数を含み,図1に示す機 能的構成をもつカオス的信号発生装置から得られる出力 信号の描くパターンを示すものである。

【図31】カオス的信号の描くパターンの他の例を示 30

【図32】カオス的信号の描くパターンのさらに他の例

【図33】カオス的信号の描くパターンのさらに他の例

【図34】カオス的信号の描くパターンのさらに他の例 を示す。

#### 【符号の説明】

10,11,12,13,14,15,1i ディレイ要素

40 20,21,22,23,24,25,21,61,62,63,64,61 初 期化要素

30,31,32,33,34,3i 非線形関数要素

40,41,42,43,44,4i 係数要素

50 加算要素

71,72,73,74,75,7i 多变数非線形関数要素

【図3】

[図 3]

【図13】 【図12】

【図23】

【図16】

【図 16 】

【図17】

【図17】

【図18】

【図 18】

【図19】

図19]

【図28】

(19)

# 【図31】

特許3210054